# MULTILEVEL INVERTER WITH FIVE LEVELS AND ONE CAPACITOR FOR GRID-CONNECTED PV SYSTEMS

<sup>1</sup>T.Lavanya, <sup>2</sup>A.Kurmaiah, <sup>3</sup>K.Swapna Rani, <sup>4</sup>K.Manikanth

<sup>1,2,3</sup>Assistant Professor, <sup>4</sup>UG Student, <sup>1,2,3,4</sup>Department of Electrical and Electronics Engineering,

Visvesvaraya College of Engineering & Technology, Hyderabad, India.

#### **Abstract**

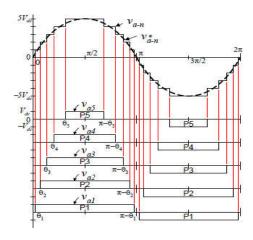

Power electronic converters are widely used in low-power Renewable Energy Generation Systems (REGS). A new application for a single phase grid linked one capacitor boost multilevel inverter in REGS is suggested in this study. Multilevel inverter systems are a good fit for medium and high power applications. This paper describes a novel five-level (2Vdc, V dc, 0, V dc, 2Vdc) boost multilevel inverter based on a single capacitor. The suggested single-phase configuration contains one dc source, eight switches, and one capacitor. The inverter operates on charge-pump theory to give boosting capability, with the capacitor charging in parallel and discharging in series connections to provide a larger output voltage. The proposed configuration requires simplecontrol tasks, and for this purpose, level-shift pulse width modulation strategy, where the reference signal is compared with four carriers, is implemented to drive the switches and generates the required pulses pattern. The developed inverter has some distinct features like the usage of only one dc-source and one-capacitor, compact size, simple control requirements and boosting ability. The system is simulated with MATLAB/ Simulation is developed to verify the performance of the developed five-level configuration gridconnected solar system.

## INTRODUCTION

In renewable energy systems, dc to ac conversion is usually necessary to provide an alternating current output with a certain amplitude, frequency, and harmonic profile. The most common ac/dc power electrical interfaces are pulse width modulation (PWM) inverters with two or more levels. They allow for the regulation of the output voltage's amplitude, frequency, and harmonics. The ac output of multilevel inverter designs has lower harmonic components. As a result of its benefits, such as decreased filter size and enhanced output waveform, multilayer inverter topologies have received substantial coverage in the literature [1–9]. Multiple dc levels are utilized in a multilayer inverter to generate a staircase waveform using power semiconductors. Multilevel inverters outperform two-level conventional inverters in terms of harmonic profile and semiconductor voltage stresses. [10]. The power quality of multilevel inverter improves with the increase in levels. On the opposite side, increasing the levels leads to a large number of power semiconductors and associated driving circuitries. Hence, system cost and complexity are high. This affects system reliability and efficiency [10, 11]. Various multilevel inverter configurations were developed. Those configurations include neutral point clamped (NPC), cascaded H- bridge (CHB), flying capacitor (FC) and modular multilevel converters [12-15]. Those multilevel schemes can be configured to generate 3, 5, 7, or nlevel output voltage [16]. NPC inverter was introduced by Akira Nabae and Akagi [17], as a three-level diode clamped form for motor drive. Stability and balancing of the dc-capacitors are a big concern of this topology, although it has only one dc- source. As the dc-capacitors are fed by the dc-source, capacitor voltage and current are controlled to keep the stability and balance of the two stacks [18]. Instead of clamping diode, Stillwell and Pilawa- Podgurski [19] used a FC to clamp the voltage of one capacitor voltage-level, which is a FC multilevel converter. FC multilevel inverter owns some distinct feature over the NPC counterpart, which are the phase redundancies. Such feature gives the FC flexibility in charging or discharging, and overcome voltage unbalance or faults.

Moreover, redundancy improves voltage stresses across the power switches and harmonic profile. Meanwhile FC multilevel inverter suffers from differentdrawbacks such as control complexity to manoeuvre voltage of all capacitors and poor switching efficiency [15, 18]. Another formation of multilevel inverter is

the CHB multilevel converter, which is built by series-connected h-bridge inverters. Each bridge has its dc-source. The modularity of this formation gives it an obvious advantage over neutral point and FC configurations; it gives the inverterhigh flexibility in fault tolerance and low power level operation after cell failure [20]. Scalable technology or modular multilevel inverter is another powerconfiguration of multilevel inverters. Where sub modules with independent control systems are connected in cascade formation to generate any number of levels required. However, current circulation within the converter increases the overall conduction losses of the system and balancing the sub module capacitor is the main issue in controlling the modular multilevel topologies. This manuscript presents a new five-level boost inverter. Different five-level configurations are presented in the literature. Five-level formation presented in [21], can generate five-level output with six switches, two diodes and two capacitors. Although it has less number of switches, it requires a complex control algorithm for balancing the capacitors and diodes, deteriorating overall system efficiency.

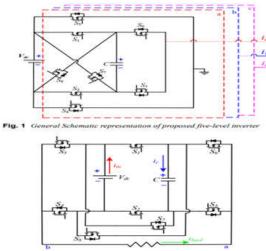

The configuration presented in [22] is similar to the one presented in [21], as it is based on the switched capacitors cell, but designed to generate nine levels instead of five levels. Roy et al. [23] developed a crossswitched inverter based on switched-capacitor-converters, it utilizes an optimum number of switches, however, its five-level version includes two capacitors, which would lead to more control complexity. Another distinct five- level topology is presented in [24]. However, it requires seven-switches, four- diodes, and two capacitors to generate the required five-level output. The new proposed configuration is a modification of the multilevel inverter configurations proposed in [25, 26]. Topologies presented in [25, 26] can generate nine-level but requires two dc sources with different voltage amplitude and in case of threephase configuration, it requires six dc- sources. On the other hand, the proposed version in this study can generate a five- level output voltage with only one dc- source and one capacitor and in three phase configuration, still, one dc source is enough to implement the three-phase output voltage. Another advantage of the proposed configuration over its counterpart in [25, 26] is its boosting ability, where the output voltage is higher than twice the input voltage. The proposed configuration generates five-level output voltage with amplitude double of the input voltage using only one dc-source, one-capacitor and eight power switches. Generated output voltage levels are (2Vdc, Vdc, 0, -Vdc, -2Vdc). The general schematic representation of the proposed system isdepicted in Fig. 1.

The system can be extended to the three-phase version by using three capacitors, and 24 power switches. In this study only single-phase configuration will be studied and investigated. The capacitor is connected in parallel in some states withthe dc-source to be charged. Then it is reconnected to be in series with the dc-source to generate 2Vdc output voltage level. To drive the switches of the multilevel inverter, level-shift PWM (LS- PWM) is implemented in this study. The reference voltage is compared with four carriers to generate the required switching states. The study is organized as follows: Section 2 discusses operation modes of the developed multilevel boost-inverter. Section 3 discusses the modulation strategy while Section 4 considers calculation of the losses by the proposed configuration and Section 5 includes simulation and experimental results.

Fig.1. single phase configuration of the proposed five level inverter

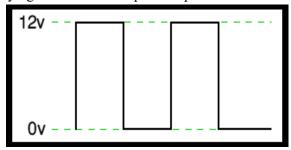

## PULSE WIDTH MODULATION

**Pulse Width Modulation** (PWM) is the most effective means to achieve constant voltage battery charging by switching the solar system controller's power devices. When in PWM regulation, the current from the solar array tapers according to the battery's condition and recharging needs Consider a waveform such as this: it is a voltage switching between 0v and 12v. It is fairly obvious that, since the voltage is at 12v for exactly as long as it is at 0v, then a 'suitable device' connected to its output will see the average voltage and think it is being fed 6v

- exactly half of 12v. So by varying the width of the positive pulse - we can vary the 'average' voltage.

#### **Pulse Width modulator**

So, how do we generate a PWM waveform? It's actually very easy, there are circuits available in the TEC site. First you generate a triangle waveform as shown in the diagram below. You compare this with a d.c voltage, which you adjust to control the ratio of on to off time that you require. When the triangle is above the 'demand' voltage, the output goes high. When the triangle is below the demandvoltage, the

## MULTI LEVEL INVERTER

An inverter is an electrical device that converts direct current (DC) to alternating current (AC) the converted AC can be at any required voltage and frequency with the use of appropriate transformers, switching, and control circuits. Static inverters have no moving parts and are used in a wide range of applications, from small switching power supplies in computers, to large electric utility high voltage direct currentapplications that transport bulk power. Inverters are commonly used to supply AC power from DC sources such as solar panels or batteries. The electrical inverter is a high power electronic oscillator. It is so named because early mechanical AC to DC converters were made to work in reverse, and thus were "inverted", to convert DC to AC.

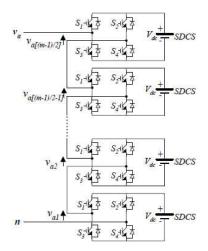

## **Cascaded H-Bridges inverter**

A single phase structure of an m-level cascaded inverter is illustrated in Figure. Each separate DC source (SDCS) is connected to a single phase full bridge, or H-bridge, inverter. Each inverter level can generate three different voltageoutputs,  $+V_{dc}$ , 0, and  $-V_{dc}$  by connecting the DC source to the ac output by different combinations of the four switches,  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ . To obtain  $+V_{dc}$ , switches  $S_1$  and  $S_4$  are turned on,

whereas -V<sub>dc</sub> can be

Fig.Single-phase structure of amultilevel cascaded H-bridges inverter

obtained by turning on switches S2 and S3.

By turning on  $S_1$  and  $S_2$  or  $S_3$  and  $S_4$ , the output voltage is 0. The AC outputs of each of the different full bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs. The number of output phase voltage levels m in a cascade inverter is defined by m = 2s+1, where s is the number of separate DC sources. An example phase voltage waveform for an 11 level cascaded H-bridge inverter with 5 SDCSs and 5 full bridges is shown in Figure. The phase voltage

+

$$v_{an} = v_{a1} + v_{a2} + v_{a3}$$

$v_{a4} + v_{a5}$  ...(4.1)

For a stepped waveform such as the one depicted in Figure 4.2 with s steps, the Fourier Transform for this waveform follows

$$V(\omega t) = \frac{4V_{de}}{\pi} \sum_{n} [\cos(n\theta_1) + \cos(n\theta_2) + \dots + \cos(n\theta_n)] \frac{\sin(n\omega t)}{n}, \text{ where } n = 1,3,5,7\dots$$

$$\dots (4.2)$$

Fig. Output phase voltage waveform of an 11 level cascade inverter with 5 separate dc sources.

## PROPOSED SYTEM AND CONTROL DESIGN

## Proposed five-level boost multilevel inverter

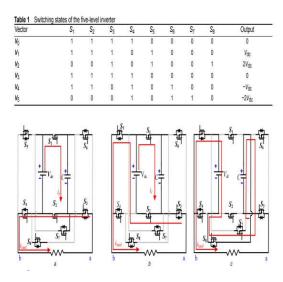

The proposed five-level boost multilevel inverter is depicted in Fig. 2. The proposed topology is a five-level

multilevel inverter with boosting ability and the output voltage is double the input voltage. The developed topology has only eight switches, two of them are without anti-parallel diode. Although the proposed inverter has 28 possible switching states, only six valid switching states are implemented, as discussed in Table 1, to generate the five-level output voltage. All valid operation modes are depicted in Figs.

3 and 4. 2.1 Operation modes Mode 1, freewheeling occurs: the inverter generatesoutput voltage equal to zero and capacitor C is charging from the dc-source (see Fig. 3a). During this analysis the capacitor is assumed to be charged when the capacitor voltage is zero, large inrush current is drawn. Indeed, most of the multilevel topologies with FCs would suffer from the same concern. In high power applications, a precharge device could be adopted, which allows capacitor voltage to build up gradually [27–32]. S1, S2, S3 and S4 are on, while the other switches are off. Capacitors C is charging from the dc source and has a voltage equal to the dc-source voltage. Capacitor C is charged from the input voltage and its steady-state value equals the input voltage. Output terminal a is connected to output terminal

b. Mode 2: the inverter generates output voltage equals to the input voltage (see Fig. 3b), S1, S2, S3 and S5 are on, while the other switches are off. Capacitors C is charged from the dc source and has its voltage equal to the dc-source voltage. Output positive terminal b is connected to the positive terminal of the input source, while the terminal a is connected to the negative terminal of the desource. Mode 3: the inverter generates output voltage, which is equal to twice the input voltage (see Fig. 3c), switches S3, S5 and S8 are on, while the other switches are off. Output positive terminal b is connected to the positive terminal of the dc-source, while terminal a is connected to the negative terminal of capacitor C. Mode 4, freewheeling occurs: the inverter generatesoutput voltage equal to zero and capacitor C is charged from the dc-source (see Fig. 4a). S1 , S2, S3 and S4 are on, while the other switches are off. C is charged from the dc source and has its voltage equal to the dc-source voltage. C is charged from the input voltage and it's steady-state value is equal to the input voltage. Output terminal b is connected to output terminal a. Mode 5: the inverter generates output voltage, which is equal to the input voltage(see Fig. 4b), S1, S2, S4 and S6 are on, while the other switches are off. C is charging from the dc source and has a voltage equal to the dc-source voltage. Output positive terminal b is connected to the negative terminal of the dc-source, while terminal a is connected to the positive terminal of the dc-source. Mode 6: the inverter generates output voltage equals to twice the input voltage (see Fig. 4c), S4, S6 and S7 are on, while the other switches are off. Output positive terminal b is connected to the negative terminal of the dc-source, while terminal a is connected to the positive terminal of capacitor C. 2.2 Parameter design The selection of capacitance is important to ensure lower ripple amount on the capacitor voltage, large ripple in capacitor voltage may cause asymmetry in output voltage steps. According to the analysis in Figs. 3a, b and 4a, C is paralleled with the dc source and is charged. This leads to the following characteristic equations:

$$\{v_{\rm c} = v_{\rm dc} \Leftrightarrow i_{\rm c} = i_{\rm in} \tag{1}$$

In mode displayed in Fig. 4a, C is still being charged. However, its current equation is different from the previously mentioned equation and it could be markedas

$$\{v_{c} = v_{dc} \Leftrightarrow i_{c} = i_{in} - i_{load}$$

(2)

C is discharging in modes described in Figs. 3c and 4b, and capacitor characteristics equation during these modes is

$$\{v_{\rm c} = v_{\rm o} - v_{\rm dc} \Leftrightarrow i_{\rm c} = i_{\rm in} \tag{3}$$

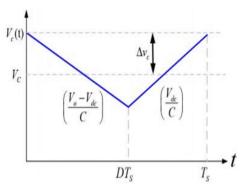

A graph of capacitor voltage is depicted in Fig. 5. From the graph and (1–3), C could be selected as follows:

Fig. operation modes

As indicated, C depends on the input voltage vdc, the output voltage vo ,sampling time Ts , accepted amount of ripple in capacitor voltage  $\Delta vc$  , and the duty ratio D. The voltage and current stresses of components are summarised in Table 2. All the switching devices have similar current stresses. However, different voltage

$$C = \left(\frac{v_{\rm o} - v_{\rm dc}}{2\Delta v_{\rm c}}\right) DT_{\rm s} \tag{4}$$

stresses are observed. S7 and S8 exhibit the highest voltage stress, which equals the output voltage. Other switches are having voltage stress equal to the input voltage. It should be noted that due to the circuit asymmetry, the voltage stresses of S7 and S8 are higher than that of the other switches. Thus, special attention needs to be paid in component selection.

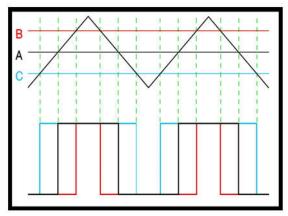

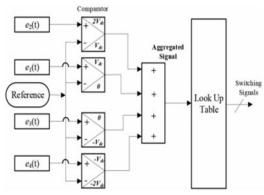

## Level shift pulse width modulation

PWM is widely used to drive the switches of power converters (dc or ac converters) at a given switching frequency. Pulses pattern generated by the PWM block isimplemented in a way to give a higher modulation index and less harmonic profile of the output waveform. Moreover, modulation schemes can be designed to reduce switching losses, current ripple, and balance capacitor voltage. In the two-level converter, a single triangular carrier is compared with the modulation signal todevelop the switching

Table.1. device voltage and current stress

| Device                                                                                                   | Voltage stress  | Current stress         |

|----------------------------------------------------------------------------------------------------------|-----------------|------------------------|

| S <sub>1</sub>                                                                                           | V <sub>in</sub> | l <sub>in</sub>        |

| S <sub>2</sub>                                                                                           | Vin             | <i>I</i> <sub>in</sub> |

| S <sub>3</sub>                                                                                           | Vin             | / <sub>in</sub>        |

| S <sub>4</sub>                                                                                           | Vin             | l <sub>in</sub>        |

| S <sub>5</sub>                                                                                           | Vin             | l <sub>in</sub>        |

| S <sub>6</sub>                                                                                           | Vin             | <i>I</i> <sub>in</sub> |

| S <sub>2</sub> S <sub>3</sub> S <sub>4</sub> S <sub>5</sub> S <sub>6</sub> S <sub>7</sub> S <sub>8</sub> | Vo              | l <sub>in</sub>        |

| S <sub>8</sub>                                                                                           | Vo              | l <sub>in</sub>        |

Fig. . Switching signal generation schematic diagram pattern of the switches.

## SIMULATION RESULTS

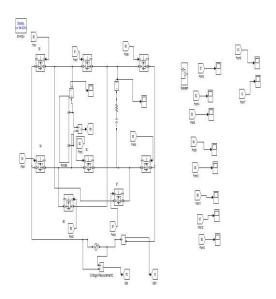

Fig .simulink model

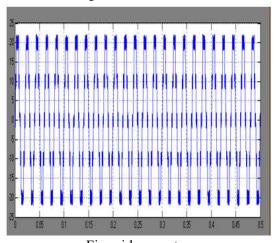

Fig grid currents

Each switching device incurs two types of losses; conduction losses whenthe device is conducting and switching losses when the device is switching (change state from off to on and vice versa). In each switching state, of the eightpossible states, at least three switches are turned on or switched to be on. This leads to two types of losses, conduction losses and switching losses. In the upcoming sections, analytical calculation for the switching and conduction losses is discussed. 4.1 Conduction losses The proposed topology has eight switches, two of its power switches and unidirectional conducting and blocking while the remaining six switches are unidirectional blocking and

Fig. Driving signal of the five level inverter

bidirectional conducting, the instantaneous conduction losses of the power switch and its body diode can be given as [14, 24]

$$\rho_{c,T}(t) = [V_T + R_T i^a(t)]i(t)$$

(5)

$$\rho_{c,D}(t) = [V_D + R_D i(t)]i(t)$$

(6)

The average conduction losses are expressed as

$$\rho_{c,avg} = \frac{1}{\Pi} \int_{0}^{\Pi} \left[ \frac{\{N_{T}(t)V_{T} + N_{D}(t)V_{D}\}i_{L}(t)}{+\{N_{T}(t)R_{T}i_{L}^{a+1}(t)\} + \{N_{D}(t)i_{L}^{2}(t)\}} \right] d(\omega t)$$

(7)

where  $\rho c, T(t)$ ,  $\rho c, D(t)$ , VT, VD, RT, RD, $\alpha$ , ND, NT and  $\rho c$ , avg(t) denote the instantaneous conduction losses of the transistor, the instantaneous conduction losses of the diode, transistor on-state voltage drop, diode instantaneous voltage drop, transistor equivalent on-resistance, diode equivalent on-state resistance, constant given by transistor characteristics, number of conducting diodes, number of conducting transistor and average conduction losses, respectively.

## **Switching losses**

Switching losses of each switching device can be estimated using a linear approximation of voltage and current during the switching period, [14, 24]. Turn-on energy losses can be calculated as

$$E_{\text{on},j} = \int_{0}^{t_{\text{on}}} \left\{ \left[ V_{\text{o},j} \frac{t}{t_{\text{on}}} \right] \left[ -\frac{t}{t_{\text{on}}} (t - t_{\text{on}}) \right] \right\} dt = \frac{1}{6} V_{\text{o},j} I t_{\text{on}}$$

(8)

Similarly, energy losses of the jth switch during turning off are calculated as

$$E_{\text{off},j} = \int_{0}^{l_{\text{off}}} \left\{ \left[ V_{o,j} * \frac{t}{t_{\text{off}}} \right] \left[ -\frac{I}{t_{\text{off}}} (t - t_{\text{off}}) \right] \right\} dt = \frac{1}{6} V_{o,j} I t_{\text{off}}$$

(9)

where Eon, j , ton, I, Vo , j Eoff, j and toff denote to turn-on loss of the jth switch, turn-on time, current through the switchafter turning on, voltage of the jth switch during turning off, turn-off loss of the jth switch, and turn-off time, respectively. Total switching power losses can be calculated as: twice the input voltage. As only one capacitor is utilized in this configuration, the balancing problem is not the issue in this configuration.

The boosting feature of the proposed inverter makes it a competitive counterpart for PV system applications. The dc capacitor is charged from the dc-source, and then it is reconfigured to be series with the dc-source. Hence higher output voltage can be obtained. To drive switches of the inverter, LS-PWM is applied. Switchingstates are designed to ensure sufficient charging period for the capacitor, and hence no big ripple in the capacitor voltage.

## **CONCLUSION**

A five-level boost multilevel inverter was presented in this study. The designed configuration for a single-phase version, made up of eight switches and only one dc-capacitor. It is capable of producing a five-level output with amplitude greater than the described system is simulated in the MATLAB/SIMULINK platform and a hardware prototype is developed in the laboratory for verification and validation. The simulation results are consistent and agree with the analytical study.

## References

- 1. M. Calais, V. G. Agelidis, L. J. Borle, and M. S. Dymond, "A transformerless five level cascaded inverter based single phase photovoltaic system," IEEE 31st Annual Power Electronics Specialists Conference, pp. 1173-1178, 2000.

- 2. M. Calais, L. J. Borle, and V. G. Agelidis, "Analysis of multicarrier PWM strategies for a single-phase five level inverter," IEEE 32nd Annual Power Electronics Specialists Conference, pp. 1351-1356, 2001.

- 3. A. Ghazanfari, H. Mokhtari, and M. Firouzi, "Simple Voltage balancing approach for CHB multilevel inverter considering low harmonic content based on a hybrid optimal modulation strategy," IEEE Trans. Power Del., Vol. 27, No. 4, pp. 2150-2158, Oct. 2012.

- 4. H. R. Teymour, D. Sutanto, K. M. Muttaqi, and P. Ciufo, "A novel modulation technique and a new balancing control strategy for a single-phase five-level ANPC converter," IEEE Trans. Ind. Appl., Vol. 51, No. 2, pp. 1215-1227, Mar. 2015.

- 5. Y. Zhang and L. Sun, "An efficient control strategy for a five-level inverter comprising flying-capacitor asymmetric H-bridge," IEEE Trans. Ind. Electron., Vol. 58, No. 9, pp. 4000-4009, Sep. 2011.

- 6. G. Ceglia, V. Guzman, C. Sanchez, F. Ibanez, J. Walter, and M. I. Gimenez, "A new simplified multilevel inverter topology for DC-AC conversion," IEEE Trans. Power Electron., Vol. 21, No. 5, pp. 1311-1319, Sep. 2006.

- 7. J. Selvaraj and N. A. Rahim, "Multilevel inverter for grid-connected PV system employing digital pi controller," IEEE Trans. Ind. Electron., Vol. 56, No. 1, pp. 149-158, Jan. 2009.

- 8. N. A. Rahim and J. Selvaraj, "Multistring five-level inverter with novel PWM control scheme for PV application," IEEE Trans. Ind. Electron., Vol. 57, No. 6, pp. 2111-2123, Jun. 2010.

- 9. J. C. Kartick, B. K. Sujit, and K. Suparna, "Dual reference phase shifted pulse width modulation

technique for a N-level inverter based grid connected solar photovoltaic system," IET Rene

ISSN: 0731-6755

Page No: 100