# DESIGN AND ANALYSIS OF MATCHLINE SENSING TECHNIQUES IN TCAM

# D.Venkata Ramana, N. Kusuma, K. Divya, K. Sampath Thanusha, R Mounika

Vignan's Institute of Engineering for Women Department of ECE, Vishakhapatnam

<u>dvrgmrit@gmail.com</u>(D.VenkataRamana),<u>naddarakusuma2002@gmail.com</u>(N.Kusuma), <u>kandreguladivya2001@gmail.com (K.Divya)</u>, <u>thanushasampth28@gmail.com</u>(K. Sampath Thanusha), <u>monikakumari922002@gmail.com</u> (R Mounika).

Abstract: The user transmits a data word to a Content Addressable Memory (CAM), which then searches its whole memory to detect if that data word is stored anywhere. This varies from normal computer memory, random-access memory (RAM), where the user supplies a memory location and the RAM returns the data word stored at that address. Binary CAMs (BiCAMs) and Ternary CAMs (TCAMs). Because they just use 1s and 0s in the word, BiCAMs are the most basic sort of CAM. Moreover, TCAMs permit a third matching state of X or "don't care" for one or more of the search word's bits. The storage reliability and sensing speed are key factors in content addressable memory performance. Match Line (ML), is used in CAM to do the sensing. An effective ML sensing method also lowers ML power consumption. Stimulation should cover up to 16 bits and demonstrate that the Resistive ML sensing improves the Capacitive ML sensing in terms of power usage as well as voltage drop between match and mismatch states.

Keywords: CAM, RAM, ML, TCAM.

## INTRODUCTION

Ternary Content Addressable Memory (TCAM) is a type of memory that is widely used in highspeed network routers and switches for fast and efficient packet forwarding. TCAMs allow for fast matching of search keys against a large number of stored patterns, making them ideal for highspeed packet processing.

The matchline sensing technique is critical to the performance of TCAMs, as it affects both the search speed and power consumption of the memory. In this project, we will design and analyze matchline sensing techniques in TCAMs, with a focus on the comparison between resistive and capacitive sensing techniques.

The resistive sensing technique uses voltage comparators to compare the stored patterns with the search key, while the capacitive sensing technique uses a set of capacitors to compare the stored patterns with the search key. Both techniques have their own advantages and disadvantages, and this project aims to compare them based on several factors such as power consumption, speed, and accuracy.

Through simulation and analysis, we will optimize the design of matchline sensing techniques in TCAMs and compare the performance of resistive and capacitive sensing techniques. The results of this project will provide valuable insights into the design and analysis of TCAMs, and help to improve the performance of high-speed network routers and switches.

## **1.1. TCAM ARCHITECTURE**

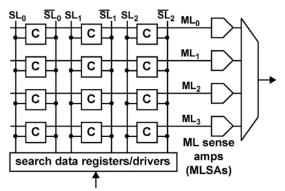

## Figure 1: TCAM Architecture

As shown in figure 1, every TCAM cell in a word line is connected to a common matchline (ML). Initially all matchlines are charged to high voltage. ML value maintains at high voltage if there is a match. Otherwise, the respective match line discharges. To start a new search, all matchlines should be at high voltage. Thus, the frequent charging and discharging happens in content addressable memories. Because of this power dissipation will be more.

TCAM is a type of memory where searches are carried out concurrently while data is organized into rows. Memory that may be addressed with content receives material as an input and outputs an address. If the stored data matches the search data, the address where the data is kept is given. The sense amplifier has access to information about matches and mismatches. Every TCAM cell in a word line is linked to a common matchline, as seen in figure 1.1. (ML). All matchlines are initially charged to a high voltage. If there is a match, ML value maintains at high voltage. If not, the corresponding matchline discharges. All match lines should be at high voltage before beginning a new search. Thus, content accessible memory experience frequent charging and discharge.

(a) Capacity: TCAM capacity can be calculated by multiplying the number of rows by the number of columns by the number of cells per column. The formula is:

Capacity = Rows x Columns x Cells per column

(b) Power: The power consumption of a TCAM can be calculated by multiplying the supply voltage by the current drawn by the TCAM. The formula is:

Power = Supply voltage x Current

(c) Delay: The delay in a TCAM is the time it takes for the TCAM to perform a search and return a result. The delay can be calculated using the formula:

Delay = (Number of rows x Search time per row) + Match time

(d) Addressing: The TCAM uses ternary addressing, which means each memory location can store a value of 0, 1, or X (don't care). The number of possible addresses in a TCAM can be calculated using the formula:

Number of addresses =  $3^{(Number of cells per row)}$

#### **1.2. NOR TCAM Architecture**

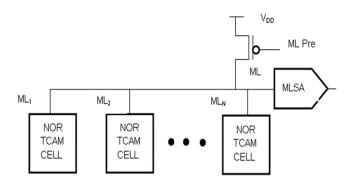

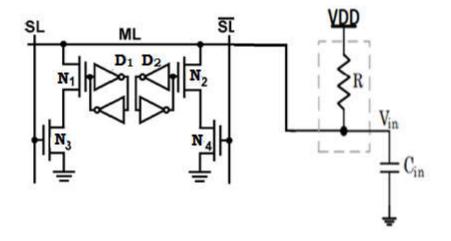

Sensing techniques aid in identifying the match and mismatch states. Sensing techniques assist in lowering the TCAM's latency and power consumption. Match lines are typically precharged at high levels when using conventional sensing techniques. Only exact matches remain high while mismatched rows remain low during the evaluation process. A row of TCAM cells with a sensing circuit can be shown in Figure 2. Here, the terms ML pre and MLSA stand for Match-Line Sensing Amplifier and NOR type TCAM cell, respectively, indicating that the Match-Line is precharged.

Figure 2: NOR TCAM Architecture

To store data in a TCAM cell of a NOR- type architecture, the data bit and the complement are stored in two SRAM cells. The don't care bit can be realized by storing "1" in both SRAM cells, that is, D1 = D2 = 1. In case of a match, both the SL-D1 and SL-D2 paths are disconnected, and the match line remains precharged.

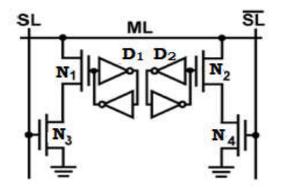

#### Figure 3: NOR -TCAM cell Table 1: Encoding of NOR cell

| Stored Value | Stored |    |  |  |

|--------------|--------|----|--|--|

|              | D1     | D2 |  |  |

| 0            | 0      | 1  |  |  |

| 1            | 1      | 0  |  |  |

| X            | 1      | 1  |  |  |

Figure 3 and Table 1 both display a NOR type TCAM cell and its encoding. Two SRAM cells are needed since the TCAM cell has three states. When D1 = 0 and D2 = 1, TCAM stores a logic "0," when D1 = 1 and D2 = 0, and don't care when D1 = 1 and D2 = 1. When SL = 0 and  $\overline{SL} = 1$ , a logic "0" is searched in TCAM. When SL = 1 and  $\overline{SL} = 0$ , a logic "1" is searched. When SL = 1 and  $\overline{SL} = 1$ , don't care is searched.

#### 2. Objectives:

The objective of "Design and Analysis of Matchline Sensing Technique in TCAM" is to analyze and compare resistive and capacitive matchline sensing techniques in TCAM in terms of accuracy, speed, and power consumption. Specifically, the project aims to:

- •Design and simulate resistive and capacitive matchline sensing circuits in a TCAM architecture.

- •Analyze the performance of resistive and capacitive matchline sensing circuits in terms of delay and power consumption.

- •Compare the performance of resistive and capacitive matchline sensing techniques in TCAM and identify the trade-offs between delay and power consumption.

- Provide insights into the design and optimization of TCAM technology for better performance and lower power consumption.

## 3. Methodology:

## 3.1. Capacitive ML Sensing Scheme:

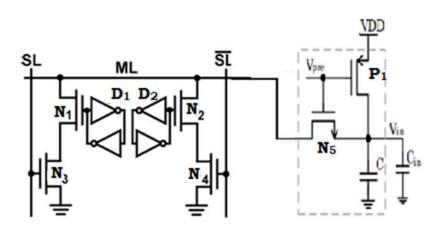

Figure 4: TCAM Cell with Capacitive Sensing Circuit

TCAM cell with Capacitive Sensing circuit. Here, a capacitor is used to differentiate between the match and mismatch states. There are two phases in its operation i.e., precharge and evaluation. During precharge phase, N5 transistor is in OFF state and P1 is in ON state so capacitor C is charged to high voltage. Moreover, in precharge phase TCAM cell is not connected to capacitor because of transistor N5. In the evaluation phase, N5 transistor is in ON state and P1 transistor is in OFF state so capacitor C tries to discharge through equivalent resistance of TCAM cell in mismatch condition and in match condition capacitor will not discharge as there is no path for capacitor.

Therefore, TCAM cell with a capacitive Sensing circuit enhances the Match-Line voltage in match case but the power consumption is more. The proposed resistive Match-Line Sensing scheme overcomes the said drawback.

#### 3.2. Resistive ML Sensing Scheme

Figure 5: TCAM Cell with Resistive Sensing Circuit

Figure 5 shows the NOR TCAM cell with Resistive Sensing circuit. For every content addressable memory, there are two cases. One is match case and the other one is mismatch case. Search operation in any content addressable memory is done in two phases. In this precharge phase, with the help of precharge transistor ML is charged too high.

Where as in the evaluation phase, according to Match-Line voltage it is identified whether it is a match case or a mismatch case. But, in this Resistive Sensing scheme, there is no need for precharge phase. From the Figure 5, it is observed that no precharge transistor is used in this resistive Sensing circuit. In the evaluation phase of the match case, Match-Line remains high and in the mismatch case, Match-Line discharges through the equivalent resistance of the TCAM cells. Resistive Sensing scheme uses a resistor as a voltage divider so the voltage that distinguish the mismatch states and the match state is depict as a voltage divider across the equivalent resistance of the TCAM cells. With the resistive Sensing circuit, the voltage at the Match-Line is enhanced when compared to the other sensing schemes. In mismatch case, Match-Line voltage is reduced at a faster rate when compared to the other sensing schemes.

While comparing Resistive Sensing design with Capacitive Sensing design, Capacitive Sensing uses a pre transistor to precharge its design. Hence, Capacitive Sensing have both precharge phase and Evaluation phase. While, in case of Resistive Sensing only evaluation phase is there so that the power consumption is comparatively lower. The speed of resistive sensing design is more compared to capacitive sensing design.

## 4. LIMITATIONS:

•Data limitations: The accuracy and reliability of your results may be limited by the data you have available. If you don't have enough data to simulate different scenarios or to validate your results, it may be difficult to draw conclusions from your analysis.

• Time limitations: Designing and analyzing matchline sensing techniques in TCAMs can be a complex and time-consuming process. Depending on the project timeline, there may be limitations on the amount of time available to fully explore all aspects of the design and analysis.

• The scope of the project is limited to the comparison of resistive and capacitive matchline sensing techniques in TCAM. Other sensing techniques and architectures may also be relevant but are not considered in this project.

• The simulation results may not perfectly reflect real-world performance due to the limitations of the simulation software and assumptions made in the circuit design.

• The project does not consider the impact of other factors such as temperature, aging, and reliability on the performance of TCAM.

• The project assumes that the memory cells in the TCAM are working correctly and do not consider the effect of errors in the memory cells on the overall performance of the system.

## 5. RESULTS:

Tanner tool is used for the implementation of the CAM. In Tanner tool the Schematic Circuit of the Content Addressable Memory can be implemented as a combination of transistors and other components. Then simulation can be done. For the comparison of Ternary Content Addressable Memory Power Consumption patterns with different Match-Line Sensing Schemes. A NOR type Ternary CAM cell with and without Match-Line Sensing Schemes are also implemented. All the implementations done on same library files and at the end power consumption of the Circuits measured and compared.

| Stored Search |      |          | TCAM with Capacitive ML<br>Sensing |           | TCAM with Resistive |            |

|---------------|------|----------|------------------------------------|-----------|---------------------|------------|

|               |      |          |                                    |           | ML Sensing          |            |

| bits          | bits | ML State | Power                              |           | Power               |            |

|               |      |          | Consumptio                         | Delay(ns) | Consump             | Delay (ns) |

|               |      |          | n (µW) at                          |           | tion (µW)           |            |

|               |      |          | 2.5V                               |           | at 2.5V             |            |

| 0             | 0    | Match    | 14.22                              | 0.29      | 12.89               | 0.26       |

| 1             | 0    | Mismatch | 13.98                              | 0.43      | 12.06               | 0.34       |

| 1             | 1    | Match    | 13.84                              | 0.49      | 13.01               | 0.46       |

| 0             | 1    | Mismatch | 14.17                              | 0.31      | 13.42               | 0.29       |

| Х             | 0    | Match    | 0.963                              | 0.52      | 0.842               | 0.49       |

| Х             | 1    | Match    | 0.852                              | 0.43      | 0.793               | 0.32       |

Table 5.1: Comparison of Power Consumption& Delay

# 6. CONLUSION:

CAMs come in two principal types: Binary CAMs (BiCAMs) and Ternary CAMs (TCAMs). BiCAMs are the simplest kind of CAM in that it uses only 1s and 0s in the stored word. TCAMs additionally permit a third matching state of X or "don't care" for one or more of the bits in the search word. The performance of content addressable reminiscence relies upon storage stability and sensing speed. In CAM, the sensing is carried out through a match line. An excellent ML Sensing technique reduces the ML strength consumption also. Simulations should carry and observe the Resistive ML Sensing has less energy consumption and the voltage drop between fit and mismatch state. The simulation and testing results demonstrate that resistive matchline sensing offers lower power consumption and faster operation than capacitive matchline sensing, especially for larger data sizes and higher input frequencies. The resistive technique is less sensitive to variations in the resistance values, which improves its accuracy and reliability.

## 7. FUTURE SCOPE:

• Integration with other memory architectures: The proposed matchline sensing technique can be integrated with other memory architectures, such as SRAM or DRAM, to improve their performance.

•Power optimization: The proposed matchline sensing technique can be further optimized for power consumption by exploring different circuit design techniques and transistor sizes.

•Testing in real-world scenarios: The effectiveness of the proposed matchline sensing technique can be evaluated in real-world scenarios, such as in data centres, where TCAMs are commonly used for packet processing and classification.

•Extension to other applications: The proposed matchline sensing technique can be extended to other applications that require high-speed and power-efficient pattern matching, such as intrusion detection systems or bioinformatics.

#### 8. CONCLUSION:

It concludes a contiguity between the capacitive and resistive sensing in TCAMs. Unlike popular pc memory, Random Access Memory (RAM), in which the user components a memory tackle and the RAM returns the data word stored at that address, a CAM is designed such that the consumer components an information word and the CAM searches its complete memory to see if that data phrase is saved somewhere in it. CAMs come in two principal types: Binary CAMs (BiCAMs) and Ternary CAMs (TCAMs). BiCAMs are the simplest kind of CAM in that it uses only 1s and 0s in the stored word. TCAMs additionally permit a third matching state of X or "don't care" for one or more of the bits in the search word. Performance of content addressable reminiscence relies upon on storage stability and sensing speed. In CAM, the sensing is carried out through match line. An excellent ML Sensing technique reduces the ML strength consumption also. Simulations should carry and observe the Resistive ML Sensing has less energy consumption and delay between fit and mismatch state.

## 9. ACKNOWLEDGEMENTS:

Our deepest thanks to our Guide Dr.D. Venkata Ramana, Associate professor, Department of Electronics and Communication Engineering, Vignan"s Institute of Engineering for Women, Visakhapatnam for his invaluable scholarly advice, inspirations, help, and guidance that helped us throughout our project work. We will always be indebted to her for all she has done for us, and it is a pleasure to acknowledge her guidance and support.

#### REFERENCES

[1] M. Rakka, et al., "Design Exploration of Sensing Techniques in 2T-2R Resistive Ternary CAMs", IEEE Transactions on Circuits and Systems II: Express Briefs (Volume: 68, Issue: 2, February 2021.

[2] M. A. Bahloul et al., "Design and analysis of 2t-2r ternary content addressable memories," in IEEE MWSCAS, Aug 2017.

[3] M. Imani et al., "Masc: Ultra-low energy multiple-access single-charge tcam for approximate computing," in 2016 Design, Automation Test in Europe Conference Exhibition (DATE), 2016.

[4] D. R. B. Ly et al., "In-depth characterization of resistive memory-based ternary content addressable memories," in 2018 IEEE IEDM, 2018.

[5] M. Imani et al., "Remam: Low energy resistive multi-stage associative memory for energy efficient computing," in IEEE ISQED, 2016.

[6] T. V. Mahendra et al., "Energy-efficient precharge-free ternary content addressable memory (tcam) for high search rate applications," IEEE TCAS I: Regular Papers, pp. 1–13, 2020.

[7] H. E. Yantır et al., "A two-dimensional associative processor," IEEE TVLSI, vol. 26, no. 9, pp. 1659–1670, 2018.

[8] H. Abunahla and B. Mohammad, Memristor Device Overview. Cham: Springer International Publishing, 2018.

[9] A. Grossi et al., "Experimental investigation of 4-kb ram arrays programming conditions suitable for tcam," IEEE TVLSI Systems, 2018.